Case Study On Barrel Shifter

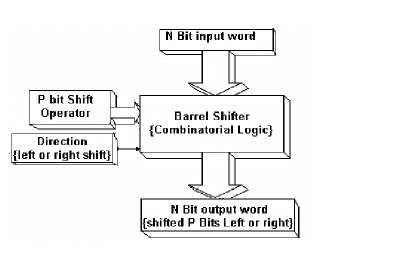

A barrel shifter is a block of combinational logic that takes an N-bit input value and provides as output the N-bit value shifted left or right by P bits. The great advantage of a barrel shifter is of course speed. It does in a single cycle what it would take P cycles to achieve in GPPs without a barrel shifter.

Right shifting in binary by P bits is really the same as division by 2P, and left shifting is the same as multiplication by 2P.

Figure illustrates the generic architecture of a barrel shifter. The main functions of a shifter in a DSP are summarized as follows:

1. Pre and/or Post scaling:

- To maintain accuracy without the benefit of a floating-point data path, fixed-point DSP processors have a good support for shifting operations. Many DSPs provide barrel shifters at both the input (pre-scaling) and output (post-scaling) of their MAC logic.

- The pre-scaler is generally activated by a pseudo instruction used in the code, for example, MACD, X, Y, 4, which divides the input data by 4 BEFORE the multiply occurs. The coefficient remains unaltered.

- An output post-scalar is generally set up prior to execution of a block of code (i.e., digital filtering, convolution, or an FFT) in order to scale the output data from the MAC operation by a specific factor.

- This is intended to reduce the probability of overflows, which can occur during long sequences of MAC operations.

- Use of this automatic scaling technique partially eliminates the overheads otherwise incurred when having to check your results for overflow and underflow (the DSP generally provides one or two flags, which need to be checked manually for overflow and underflow by your program after each MACD execution).

- If an overflow is indicated, you can either abort the program or recalculate the results.

2. Normalization & Denormalization:

- It is indicated, you can either abort the program or recalculate the results.

- Normalization involves conversion from fixed point to floating point systems by the generation of mantissa and exponent.

- This is a two process.

- The first one involves exponent detection which calculated the number of shifts needed.

- The next step provides this value to the shifter for actually shifting the number. Denormalization involves the conversion of floating point into fixed point systems i.e. the inverse of normalization.

- The exponent provides a number of shifts required in the mantissa.

3. Block floating point:

- A block floating-point format enables a fixed-point processor to gain some of the increased dynamic range of a floating-point format without the overhead needed to do floating-point arithmetic. However, some additional programming is required to maintain a block floating-point format.

- It can also be used in floating point processors.

Tips for viva and practicals

DATA ADDRESS GENERATORS

- Super Harvard Architecture with modifications is the most suited Architectures for DSPs.

- Such an architecture has multiple busses to access the memory viz. Data memory bus & program memory bus.

- This is obviously an advantage with respect to increasing in speed but this would demand additional hardware that would keep track of address on each of these busses.

- The Data Address Generator (DAGs) keeps a track of the addresses of the input data and the coefficients that are stored in the data and program memories respectively.

- Now the CPU no longer has to bother about the addresses of the data, the DAG will do that task.

- This is most useful when a set of addresses are used repeatedly, for example, scanning a data array or in FFT computations.

- The address generation unit would require its own arithmetic unit to increment or decrement the addresses, and/or to add/subtract offsets from the base address in case of non-sequential addresses.

- The increment/decrement step size for an address in each case can be predefined as 1,2,4 or 8 and so on depending upon the size of each data item. Any DAG would require at least the following types of registers. The types of registers are:

•Index registers: An index register holds an address and acts as a pointer to memory.

•Modify registers: A modify register provides the increment or step size by which an index register is pre- or post-modified during a register move.

•Length and Base registers: Length and base registers setup the range of addresses and the starting address for a circular buffer. These registers hold the values that the DAG uses for generating addresses.How to configure DSP processor

Dropdown your comments below if you want more case studies or if you want any help regarding your projects and Mini projects, I will be more than happy to help you all with your queries 🙂